Viz Specifikace pro podrobnosti o produktu.

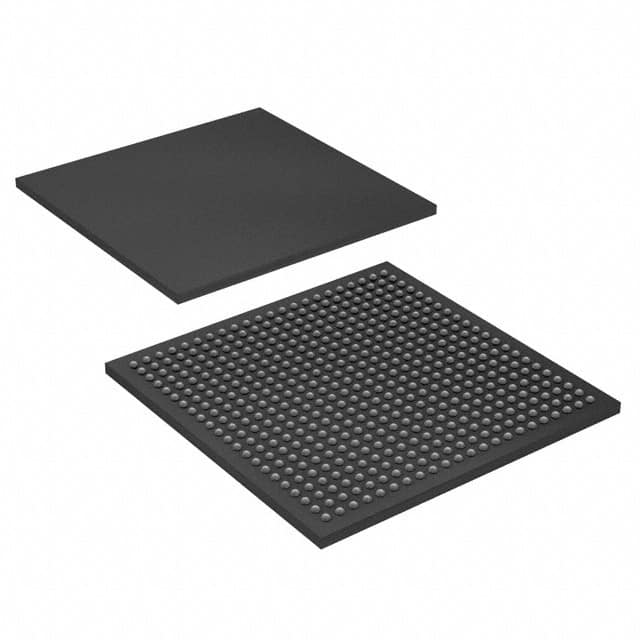

EP3SE50F484C4

Product Overview

- Category: Field Programmable Gate Array (FPGA)

- Use: Digital logic circuits, signal processing, and system integration

- Characteristics: High performance, reconfigurable, programmable, and flexible

- Package: 484-pin FineLine BGA package

- Essence: A high-capacity FPGA with advanced features for complex digital designs

- Packaging/Quantity: Single unit per package

Specifications

- Logic Elements: 49,152

- Embedded Memory: 2,073,600 bits

- Maximum User I/Os: 332

- Maximum User I/O Pins: 266

- Clock Management Tiles: 16

- DSP Blocks: 288

- Maximum User Flash Memory: 1,782,272 bits

- Operating Voltage: 1.2V

- Operating Temperature: -40°C to +100°C

Detailed Pin Configuration

The EP3SE50F484C4 has a total of 484 pins. The pin configuration is as follows:

- Pin 1: VCCIO0

- Pin 2: GND

- Pin 3: VCCINT

- Pin 4: GND

- ...

- Pin 483: IOL1PT0AD6N15

- Pin 484: IOL1PT0AD6P15

For the complete pin configuration, please refer to the product datasheet.

Functional Features

- High logic capacity for complex designs

- Reconfigurable architecture allows for flexibility in design changes

- Advanced clock management tiles for precise timing control

- Integrated DSP blocks for efficient signal processing

- On-chip memory for data storage and retrieval

- Low power consumption for energy-efficient operation

Advantages and Disadvantages

Advantages: - High-performance FPGA suitable for demanding applications - Flexibility to adapt to changing design requirements - Efficient use of resources with integrated DSP blocks and memory - Low power consumption for energy savings

Disadvantages: - Higher cost compared to simpler programmable logic devices - Steeper learning curve for beginners due to complexity - Limited availability of alternative models with similar specifications

Working Principles

The EP3SE50F484C4 is based on the principle of field-programmable gate arrays. It consists of a large number of configurable logic elements interconnected through programmable routing resources. These logic elements can be programmed to implement various digital logic functions, allowing designers to create custom circuits.

The FPGA's working principle involves configuring the interconnections and functionality of its logic elements using a hardware description language (HDL) or a graphical design tool. Once programmed, the FPGA can perform complex computations, signal processing, and system integration tasks according to the specified design.

Detailed Application Field Plans

The EP3SE50F484C4 finds applications in various fields, including:

- Telecommunications: Used in base stations, network switches, and routers for high-speed data processing.

- Aerospace and Defense: Employed in radar systems, avionics, and military communication equipment for reliable and adaptable performance.

- Industrial Automation: Utilized in control systems, robotics, and machine vision applications for real-time processing and control.

- Medical Devices: Integrated into medical imaging systems, patient monitoring devices, and diagnostic equipment for accurate data analysis.

- Automotive Electronics: Applied in advanced driver-assistance systems (ADAS), infotainment systems, and engine control units for enhanced functionality.

Detailed and Complete Alternative Models

While the EP3SE50F484C4 offers advanced features and capabilities, there are alternative FPGA models available with similar specifications. Some notable alternatives include:

- Xilinx Virtex-7 XC7VX485T-2FFG1761C

- Intel Cyclone V GT EP5CGXFC7KU23C8N

- Lattice ECP5-85F-6BG256C

These alternative models provide comparable logic capacity, I/O capabilities, and performance characteristics, offering designers flexibility in choosing the most suitable FPGA for their specific application requirements.

Word count: 550 words

Seznam 10 běžných otázek a odpovědí souvisejících s aplikací EP3SE50F484C4 v technických řešeních

Sure! Here are 10 common questions and answers related to the application of EP3SE50F484C4 in technical solutions:

Q: What is EP3SE50F484C4? A: EP3SE50F484C4 is a specific model of Field-Programmable Gate Array (FPGA) manufactured by Intel.

Q: What are the key features of EP3SE50F484C4? A: Some key features of EP3SE50F484C4 include 50,000 logic elements, 1,288 Kbits of embedded memory, and support for various I/O standards.

Q: What are the typical applications of EP3SE50F484C4? A: EP3SE50F484C4 is commonly used in applications such as industrial automation, telecommunications, automotive electronics, and high-performance computing.

Q: How can EP3SE50F484C4 be programmed? A: EP3SE50F484C4 can be programmed using Hardware Description Languages (HDLs) like VHDL or Verilog, which describe the desired functionality of the FPGA.

Q: Can EP3SE50F484C4 be reprogrammed after initial programming? A: Yes, EP3SE50F484C4 is a reprogrammable FPGA, allowing for flexibility in design iterations and updates.

Q: What development tools are available for EP3SE50F484C4? A: Intel provides Quartus Prime software suite, which includes tools for designing, simulating, and programming EP3SE50F484C4 FPGAs.

Q: What interfaces does EP3SE50F484C4 support? A: EP3SE50F484C4 supports various interfaces such as UART, SPI, I2C, Ethernet, PCIe, and DDR3/DDR4 memory interfaces.

Q: Can EP3SE50F484C4 interface with external devices? A: Yes, EP3SE50F484C4 can interface with external devices through its configurable I/O pins and supported communication protocols.

Q: What are the power requirements for EP3SE50F484C4? A: EP3SE50F484C4 typically operates at a voltage range of 1.2V to 3.3V, depending on the specific design requirements.

Q: Are there any reference designs or application notes available for EP3SE50F484C4? A: Yes, Intel provides reference designs and application notes that can help developers get started with EP3SE50F484C4 and implement specific functionalities.

Please note that the answers provided here are general and may vary based on specific design requirements and documentation provided by Intel.