Viz Specifikace pro podrobnosti o produktu.

SN74LS259BDR

Product Overview

Category

SN74LS259BDR belongs to the category of integrated circuits (ICs).

Use

This IC is commonly used for data storage and manipulation in digital systems.

Characteristics

- High-speed operation

- Low power consumption

- Wide operating voltage range

- Multiple input/output options

- Compatibility with various logic families

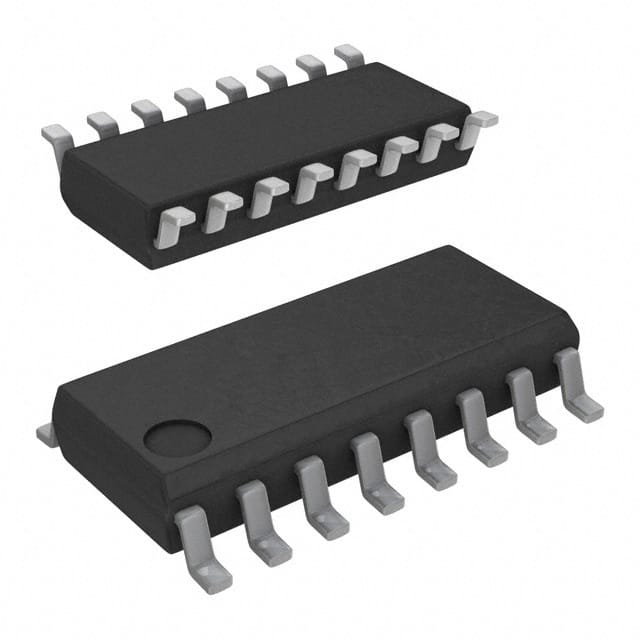

Package

SN74LS259BDR is available in a 16-pin SOIC (Small Outline Integrated Circuit) package.

Essence

The essence of SN74LS259BDR lies in its ability to store and process data efficiently, making it an essential component in many digital devices.

Packaging/Quantity

SN74LS259BDR is typically sold in reels or tubes containing multiple units. The exact quantity may vary depending on the supplier.

Specifications

- Supply Voltage: 4.75V to 5.25V

- Operating Temperature Range: -40°C to 85°C

- Input Voltage High: 2V (min), 0.8V (max)

- Input Voltage Low: 0.8V (min), 0.4V (max)

- Output Voltage High: 2.7V (min), 2.4V (max)

- Output Voltage Low: 0.5V (max)

Detailed Pin Configuration

- GND (Ground)

- D0 (Data Input 0)

- D1 (Data Input 1)

- D2 (Data Input 2)

- D3 (Data Input 3)

- D4 (Data Input 4)

- D5 (Data Input 5)

- D6 (Data Input 6)

- D7 (Data Input 7)

- MR (Master Reset)

- CE (Clock Enable)

- CP (Clock Pulse)

- Q0 (Output 0)

- Q1 (Output 1)

- Q2 (Output 2)

- VCC (Supply Voltage)

Functional Features

- Data storage and retrieval

- Parallel-to-serial data conversion

- Cascading capability for larger data storage

- Master reset functionality

- Clock enable control

Advantages and Disadvantages

Advantages

- High-speed operation allows for efficient data processing.

- Low power consumption helps conserve energy in digital systems.

- Wide operating voltage range ensures compatibility with various power sources.

- Multiple input/output options provide flexibility in system design.

- Compatibility with different logic families enables integration into diverse circuits.

Disadvantages

- Limited data storage capacity compared to other memory devices.

- Requires external clock signal for proper operation.

- Sensitivity to noise and interference may affect performance.

Working Principles

SN74LS259BDR operates based on the principles of sequential logic. It stores data in internal flip-flops and retrieves it based on clock signals. The inputs control the data to be stored, while the clock pulse determines when the data is transferred. The outputs provide the stored data in parallel or serial format, depending on the configuration.

Detailed Application Field Plans

SN74LS259BDR finds applications in various fields, including: - Microcontrollers - Digital signal processors - Communication systems - Industrial automation - Consumer electronics

Detailed and Complete Alternative Models

Some alternative models to SN74LS259BDR include: - 74HC259: Similar functionality but operates at higher voltages. - CD4023: Offers additional features like triple 3-input NAND gates. - 74FCT259: Provides faster operation and lower power consumption.

These alternative models can be considered based on specific requirements and compatibility with the existing system.

Word count: 455 words

Seznam 10 běžných otázek a odpovědí souvisejících s aplikací SN74LS259BDR v technických řešeních

Sure! Here are 10 common questions and answers related to the application of SN74LS259BDR:

Q: What is SN74LS259BDR? A: SN74LS259BDR is a 8-bit addressable latch with 3-state outputs, commonly used in digital systems.

Q: What is the purpose of SN74LS259BDR? A: SN74LS259BDR is used to store and control data in digital circuits, allowing for efficient data manipulation and storage.

Q: How many bits can SN74LS259BDR store? A: SN74LS259BDR can store 8 bits of data.

Q: What are the inputs and outputs of SN74LS259BDR? A: The inputs include data inputs (D0-D7), address inputs (A0-A2), and control inputs (G, CEP, CET). The outputs are Q0-Q7.

Q: How does SN74LS259BDR work? A: When enabled, the data on the D inputs is latched and stored in the internal registers based on the address inputs. The stored data can be accessed through the output pins.

Q: What is the function of the control inputs (G, CEP, CET)? A: The G input enables or disables the latch. CEP (Clock Enable Parallel) and CET (Clock Enable Tristate) control the clocking and tristate functions of the latch.

Q: Can SN74LS259BDR be cascaded? A: Yes, multiple SN74LS259BDR chips can be cascaded together to increase the number of addressable bits.

Q: What is the power supply voltage range for SN74LS259BDR? A: SN74LS259BDR operates with a power supply voltage range of 4.75V to 5.25V.

Q: What is the maximum clock frequency for SN74LS259BDR? A: The maximum clock frequency for SN74LS259BDR is typically around 33 MHz.

Q: What are some common applications of SN74LS259BDR? A: SN74LS259BDR is commonly used in address decoding, data multiplexing, and general-purpose digital systems where efficient data storage and control is required.

Please note that these answers are general and may vary depending on specific circuit designs and requirements.